# SERVICE MANUAL

## **NELLCOR** N-200 PULSE OXIMETER

## NOTICE:

This manual is provided for the purpose of servicing the NELLCOR N-200 pulse oximeter. It is provided without charge by Nellcor Incorporated. This manual contains unpublished proprietary information and is not to be copied, transmitted, or used for any other purpose. Additional copies are available upon request by writing the Company at the address below.

Caution: Federal law (U.S.) restricts this device to sale by or on the order of a physician.

Nellcor Incorporated 25495 Whitesell Street Hayward, California 94545 U.S.A. 415 887-5858 1-800-NELLCOR

© May1989 Nellcor Incorporated

057276A

S/N:

# TABLE OF CONTENTS

|         |                                                           | rage |

|---------|-----------------------------------------------------------|------|

| SECTION | 1-1                                                       |      |

| SECTION |                                                           | 0.1  |

| SECTION | 2. DESCRIPTION OF INSTRUMENT                              | 2-1  |

| SECTION | 3. THEORY OF OPERATION                                    | 3-1  |

| 3.1.    | GENERAL THEORY                                            | 3-1  |

|         | 3.1.1. C-LOCK ECG Synchronization                         | 3-1  |

|         | 3.1.2. Automatic Calibration                              | 3-2  |

|         | 3.1.3. Functional vs. Fractional Saturation               | 3-2  |

|         | 3.1.4. Measured vs. Calculated Saturation                 | 3-2  |

| 3.2.    | CIRCUIT-LEVEL DESCRIPTION                                 | 3-3  |

| 3.3.    | PATIENT MODULE                                            | 3-3  |

| 3.4.    | PROCESSOR PCB                                             |      |

|         | 3.4.1. Digital Section                                    | 3-4  |

|         |                                                           |      |

|         | 3.4.1.2. Memory Map         3.4.1.3. Wait State Generator | 3-5  |

|         | 3.4.1.3. Wait State Generator                             | 3-5  |

|         | 3.4.1.4. Clock Generator                                  | 3-5  |

|         | 3.4.1.4. Clock Generator                                  | 3-5  |

|         | 3.4.1.6. Pattern Generator                                | 3-6  |

|         | 3.4.2. Analog Front End and LED Current Drive             | 3-6  |

|         | 3.4.2.1. Main Analog Signal Flow                          | 3-6  |

|         | 3.4.2.2. Sync Detector                                    | 3-6  |

|         | 3.4.2.3. Demultiplexer                                    | 3-6  |

|         | 3.4.2.4. Logic Flags                                      | 3-7  |

|         | 3.4.2.5. LED Drive Circuitry                              | 3-7  |

| -       | 3.4.3. ECG Front End                                      | 3-8  |

|         |                                                           | 0"0  |

|         | 3.4.3.2. Offset Amplifier                                 | 3-8  |

|         | 3.4.3.2. Offset Amplifier                                 | 3-8  |

|         | 3.4.3.4. Power Line Frequency Sensing                     |      |

|         | 3.4.4. A:D/D:A Subsection                                 | 3-9  |

|         | S.4.4.1. A.D COnversion                                   |      |

|         | 3.4.4.2. D:A Conversion                                   | 3-10 |

|         | 3.4.5. Timing and Control                                 | 3-10 |

|         | 3.4.5.1. Polled Processor Flags                           | 3-10 |

|         | 3.4.5.2. Interrupt Processor Flags                        | 3-11 |

| 3.5.    | FRONT PANEL DISPLAY                                       | 3-11 |

| ÷.,     | 3.5.1. Driver PCB                                         | 3-11 |

|         |                                                           | 0-16 |

|         | 3.5.1.2. Lightbar Drivers                                 | 3-12 |

|         | 3.5.1.3. Front Panel Controls                             | 3-12 |

|         | 3.5.1.4. Power-Up Display Element Test                    | 3-13 |

|         | 3.5.1.5. Speaker Driver Circuit                           | 3-13 |

|         | 3.5.2. Display PCB                                        | 3-13 |

| 3.6.    |                                                           | 3-13 |

| 3.7.    |                                                           | 3-14 |

|         | 3.7.1. ON/STDBY Control Circuit                           | 3-14 |

|         | 3.7.1.1. ON State                                         | 3-14 |

|         | 3.7.1.2. ON to STDBY                                      | 3-14 |

|         | 3.7.1.3. STDBY State                                      | 3-15 |

|         | 3.7.1.4. STDBY to ON State                                |      |

|         | 3.7.1.5. Voltage Regulator                                |      |

| · .     | 3.7.1.6. Power-On Time Delay                              | 3-15 |

| 1       | 3.7.2. Battery Charger Circuit                            | 3-15 |

5

| ÷.,                   | 3.8.       | POWE    | 3-15                                                                                               |             |

|-----------------------|------------|---------|----------------------------------------------------------------------------------------------------|-------------|

|                       |            | 3.8.1.  | RBASE                                                                                              | 3-16        |

|                       |            | 3.8.2.  | Upper and Lower Daughter PCBs                                                                      | 3-16        |

|                       | ,          |         | 3.8.2.1. Upper Daughter PCB                                                                        | 3-16        |

| · · · · ·             |            |         | 3.8.2.2. Lower Daughter PCB                                                                        | 3-17        |

|                       |            | 3.8.3.  | Middle Daughter PCB                                                                                | 3-17        |

|                       |            |         | Middle Daughter PCB                                                                                | 3-17        |

|                       |            |         | 3.8.3.2. ECG Output                                                                                | 3-18        |

|                       |            |         |                                                                                                    |             |

|                       | SECTION    | 14. TRC | DUBLESHOOTING AND ASSEMBLY GUIDE                                                                   | 4-1         |

|                       | 4.1.       | INITIA  | L TROUBLESHOOTING PROCEDURES                                                                       | 4-1         |

|                       | 4.2.       | DETAI   | ILED TROUBLESHOOTING PROCEDURES                                                                    | 4-6         |

|                       |            | 4.2.1.  | Failure Modes                                                                                      | 4-6         |

|                       |            | 4.2.2.  | Troubleshooting Summary                                                                            | 4-7         |

|                       |            |         | 4.2.2.1. Monitor                                                                                   | 4-7         |

|                       |            |         | 4.2.2.2. Powerbase<br>FOR DISASSEMBLY AND REASSEMBLY<br>Top Cover Removal                          | 4-10        |

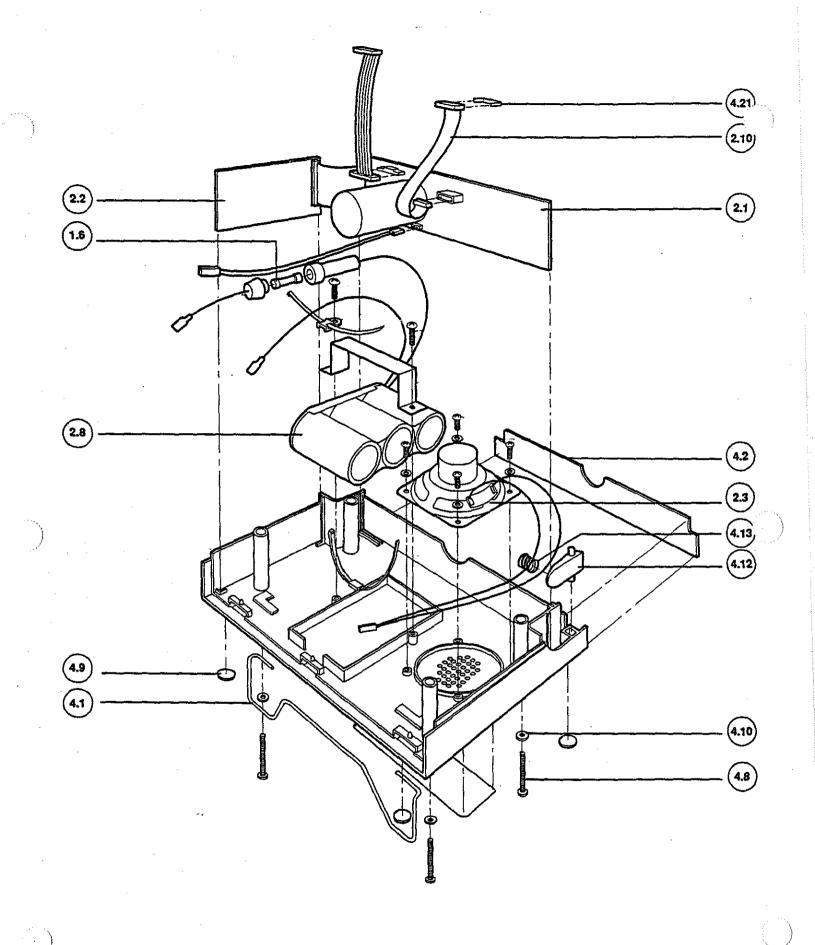

|                       | 4.3.       | MONIT   | OR DISASSEMBLY AND REASSEMBLY                                                                      | 4-10        |

|                       |            |         | Top Cover Removal                                                                                  | 4-10        |

|                       |            | 4.3.2.  | Power Supply PCB and Battery Charger PCB Removal                                                   | 4-11        |

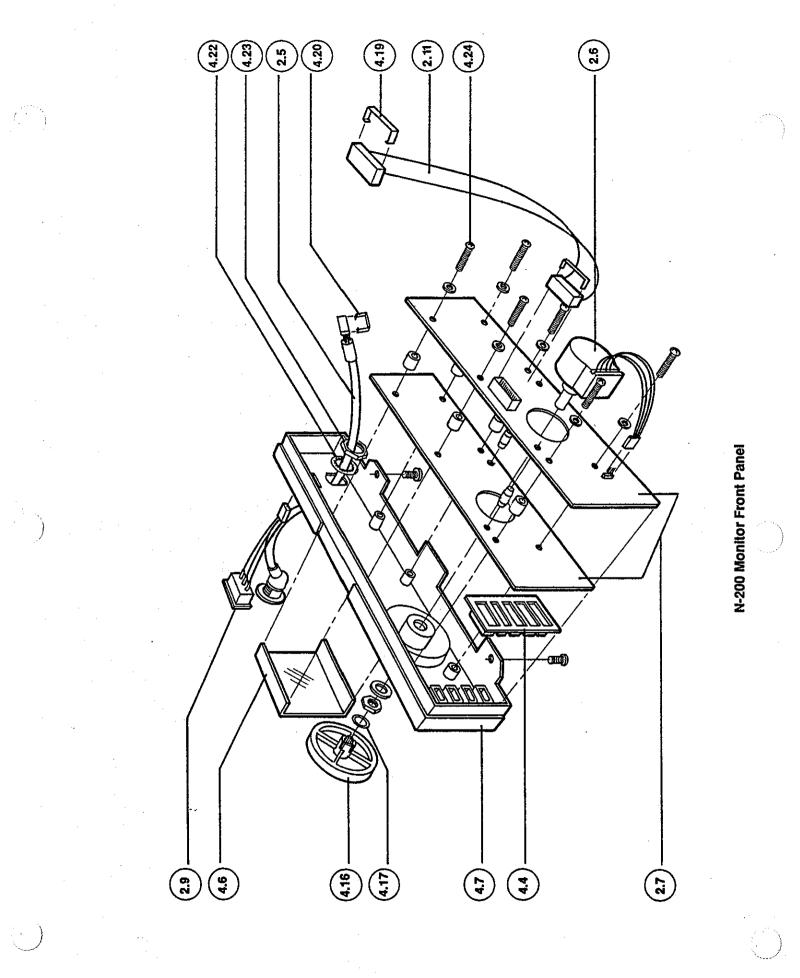

|                       |            | 4.3.3.  | Front Panel Removal                                                                                | 4-12        |

|                       |            | 4.3.4.  | Front Panel Removal<br>Display PCB and Driver PCB Removal<br>Battery Pack Removal/Fuse Replacement | 4-13        |

|                       |            | 4.3.5.  |                                                                                                    |             |

|                       |            | 4.3.6.  |                                                                                                    | 4-13        |

|                       |            | 4.3./.  | Top Cover Replacement                                                                              | 4-13        |

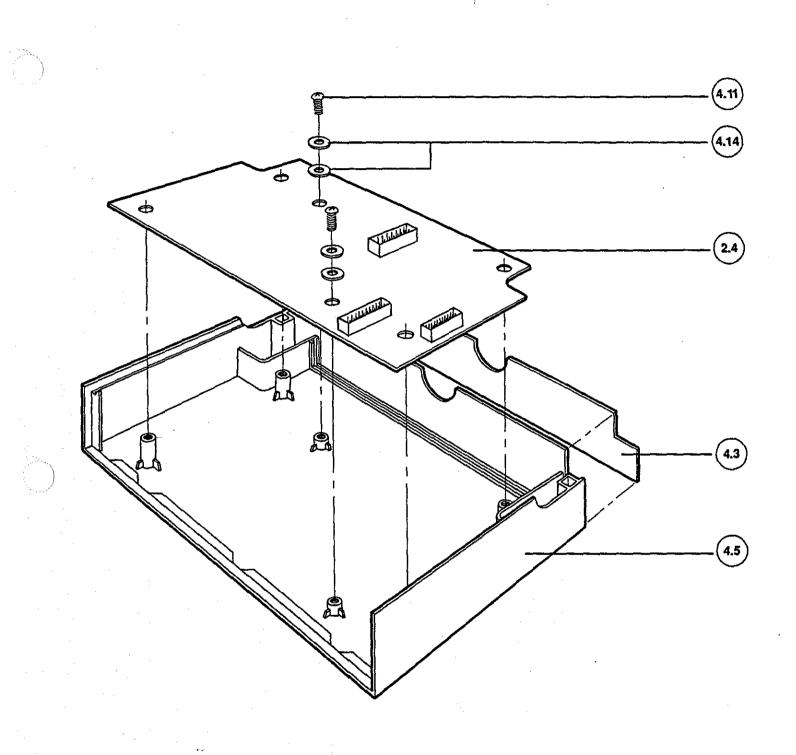

|                       | 4.4.       |         | AC Euro Deplement                                                                                  | 4-14        |

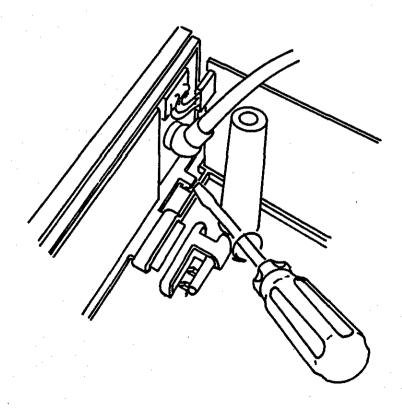

|                       |            | 4.4.1.  | AC Fuse Replacement                                                                                | 4-14        |

|                       |            | 4.4.2.  | Powerbase Disassembly                                                                              | 4-10<br>    |

|                       |            | 4.4.J.  | PCB Removal Powerbase Reassembly                                                                   | 4-15<br>4+E |

| )                     |            | ·····   |                                                                                                    | 4-13        |

|                       | SECTION    | 5. TES  | STING AND CALIBRATION                                                                              | 5-1         |

|                       | 51         |         |                                                                                                    | 5 1         |

|                       | 5.2.       | REQU    |                                                                                                    | 5-2         |

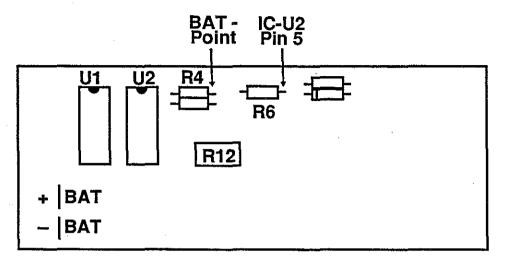

|                       | 5.3.       | BATTE   | RY CHARGER PCB TESTS                                                                               | 5-2         |

|                       |            | 5.3.1.  | Raw DC Voltage                                                                                     | 5-2         |

|                       |            | 5.3.2.  | Battery Charging Voltage                                                                           | 5-3         |

|                       |            | 5.3.3.  | Low Battery/Instrument Shut-Off Voltages                                                           | 5-3         |

|                       |            | 5.3.4.  | ON/STDBY Switch Test                                                                               | 5-4         |

|                       |            | 5.3.5.  | Battery Operation                                                                                  | 5-5         |

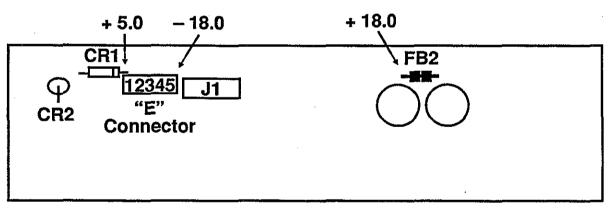

|                       | 5.4.       | REGU    | LATED POWER SUPPLY PCB TESTS                                                                       | 5-5         |

|                       | 5.5.       | PROC    | ESSOR PCB TESTS Processor PCB Voltage Regulation                                                   | 5-6         |

|                       |            | 5.5.1.  | Processor PCB Voltage Regulation                                                                   | 5-6         |

|                       |            | 5.5.2.  | Calibration Resistor Determination                                                                 | 5-7         |

| •                     |            | 5.5.3.  | LED Intensity Control                                                                              | 5-7         |

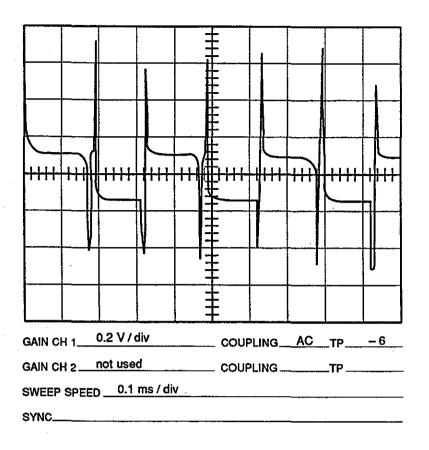

|                       |            | 5.5.4.  | Input Amplifier (INAMP) Automatic Gain                                                             | 5-8         |

|                       |            | 5.5.5.  | Sync Detector Alignment                                                                            | 5-8         |

|                       |            | 5.5.6.  | IR Channel Gain                                                                                    | 5-9         |

|                       |            | 5.5.7.  | RED Channel Gain                                                                                   | 5-9         |

|                       |            | 5.5.8.  | ECG Processor                                                                                      | 5-9         |

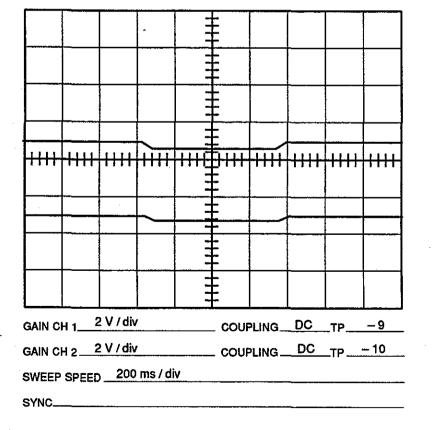

|                       |            | 5.5.9.  | A:D/D:A Alignment                                                                                  | 5-11        |

|                       | <b>F</b> • |         | Clock/Calendar Lithium Battery Test                                                                | 5-12        |

|                       |            |         |                                                                                                    |             |

|                       | 5.7.       |         | EM FUNCTION TEST                                                                                   |             |

|                       |            | 5.7.1.  | AC Operation                                                                                       |             |

|                       |            | 5.7.2.  | Battery Operation                                                                                  | 5-14        |

| x, <sub>440</sub> 4** |            | 5.7.3.  |                                                                                                    |             |

|                       |            | 5.7.4.  | Pocket Tester Operation                                                                            | 5-14        |

.

|               | 5.7.5. Adjusting Alarm Limits                           | 5-15 |

|---------------|---------------------------------------------------------|------|

|               | 5.7.6. Temporary Alarm Silence                          | 5-16 |

|               | 5.7.7. Disabling the Audible Alarm                      | 5-16 |

|               | 5.7.8. Powerbase-to-Monitor Communication               | 5-16 |

|               | 5.7.9. Monitor-to-Powerbase Communication               | 5-16 |

|               | 5.7.10. Middle Daughter PCB Verification                | 5-17 |

|               | Attachment 1                                            |      |

|               | Attachment 2                                            | 5-19 |

|               | Attachment 3                                            | 5-20 |

| SECTION       | 6. ADDITIONAL SERVICE INFORMATION                       | 6-1  |

| SECTION       | 7. PACKING FOR SHIPMENT<br>REPACKING IN ORIGINAL CARTON | 7-1  |

| 7.1.          | REPACKING IN ORIGINAL CARTON                            | 7-1  |

| 7 <b>.2</b> . | PACKING IN DIFFERENT CARTON                             | 7-1  |

| SECTION       | 8. SPARE PARTS                                          | 8-1  |

| 8.1.          | EXTERNAL PARTS                                          | 8-1  |

| 8.2.          | ELECTRICAL ASSEMBLIES                                   | 8-1  |

|               | 8.2.1. Monitor                                          | 8-1  |

|               | 8.2.2. Powerbase                                        | 8-1  |

| 8.3.          | MECHANICAL PARTS                                        | 8-2  |

|               | 8.3.1. Monitor                                          | 8-2  |

|               | 8.3.2. Powerbase                                        | 8-2  |

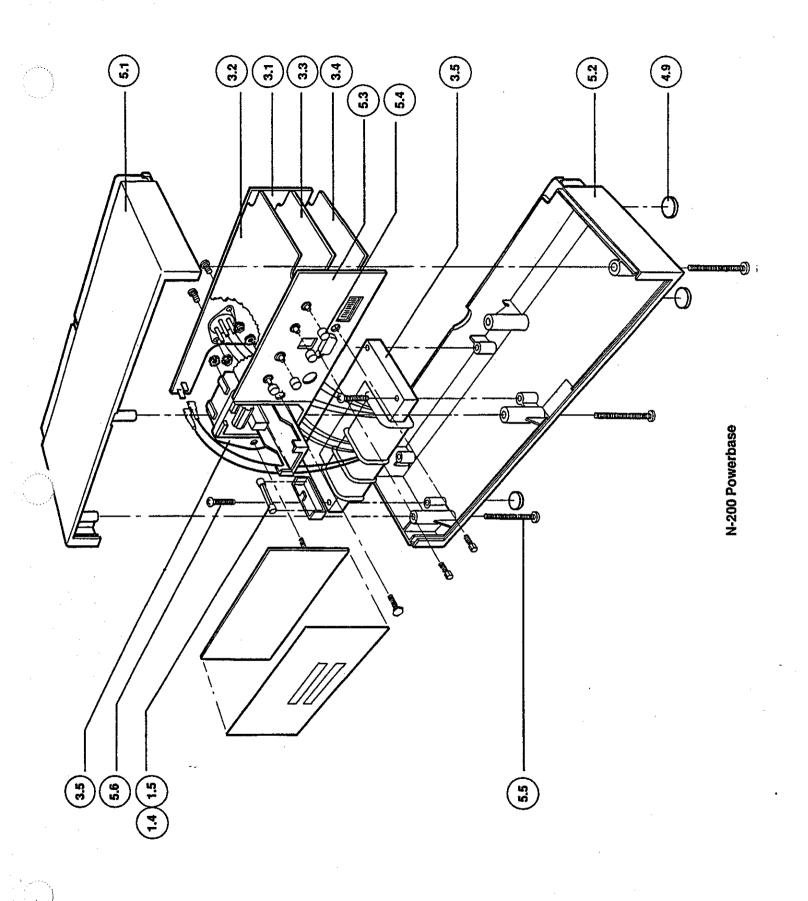

| 8.4.          | CHASSIS-LEVEL ASSEMBLY VIEWS                            | 8-3  |

| SECTION       | 9. SCHEMATIC DIAGRAMS                                   | 9-1  |

|               | 10. INDEX                                               | 10-1 |

NELLCOR, OXIBAND, and DURASENSOR are U.S. registered trademarks of Nellcor Incorporated. OXISENSOR and C-LOCK are U.S. trademarks of Nellcor Incorporated.

. .

WARNING: The NELLCOR N-200 pulse oximeter contains no user-servicable parts. For protection against electrical hazard, refer all servicing to qualified personnel.

WARNING: For continued protection against fire hazard, replace fuses only with the same type and rating.

WARNING: The *NELLCOR* N-200 pulse oximeter is a patient-connected medical device. An isolated patient connector is provided to protect the patient from potentially dangerous electrical potentials or ground paths. To protect the integrity of this connection, the procedures and part specifications contained in this manual must be adhered to.

.

## **SECTION 1**

#### INTRODUCTION

This manual covers test and repair of the *NELLCOR*• N-200 pulse oximeter. The N-200 is identified by its two-piece construction. The front part of the N-200 is the monitor; the back part of the N-200 is the powerbase. The monitor receives, processes, and stores patient pulse data; the powerbase provides AC power to the monitor and drives peripheral display and recording devices. Communication between monitor and powerbase is provided by a bi-directional optical link.

This manual is provided to qualified service personnel for the purpose of maintaining and repairing the *NELLCOR* N-200 pulse oximeter. Dangerous voltages are exposed when the cover is removed, certain components are critical to maintain patient isolation, and improper repair procedures can adversely affect the instrument's calibration. For the protection of service personnel and patients, the procedures described in this manual are only to be performed by qualified service personnel.

Repair and testing of the instrument exposes service personnel to potentially hazardous voltages, and improper repair or adjustment may affect the accuracy or patient protection associated with the instrument. Where appropriate, warnings or cautions have been included in the text of this manual. The term "WARNING" is used to bring attention to a procedure or precaution that is important to ensure the safety of the service personnel or possibly the patient. The word "CAUTION" brings attention to a procedure that should be carefully followed in order to prevent damage to the instrument or an error in calibration or performance. It is important that these warnings and cautions be read carefully and followed.

# .

(a) A set of the se

## **SECTION 2**

## DESCRIPTION OF THE INSTRUMENT

The NELLCOR N-200 pulse oximeter is intended for continuously monitoring arterial oxygen saturation and pulse rate. The measurement is made noninvasively by applying a reusable clip-on or disposable adhesive-attached sensor to a finger or other site on the patient to be monitored.

The instrument is a portable unit, weighing about 8 pounds total, with a self-contained battery intended for operation for periods of up to 2 hours during power failures or transport. The battery is recharged whenever the unit is connected to AC power, and is fully recharged in 14 hours.

Front panel controls allow adjustment of the beeper volume, alarm volumes, alarm disabling, and adjustment of alarm limits for high and low oxygen saturation, and high and low pulse rate. A connector is located on the front panel for connection of the patient module assembly. The standard patient cable is 4 meters in length and is terminated by a module containing a preamplifier and sensor and ECG connectors. The entire patient module assembly is isolated from ground with a maximum leakage current of 10 microamperes. This provides safety for the patient from currents generated by faulty equipment, e.g., defibrillators or electrosurgical units.

WARNING: To assure continued patient safety, the patient module or sensors must not be replaced with any parts other than those designated or manufactured by Nellcor Incorporated.

A number of patient safety and labor-saving features are incorporated into the N-200:

- C-LOCK<sup>\*\*</sup> ECG synchronization enhances performance in high-motion environments, such as the ICU or the NICU.

- Three operating modes provide different averaging times, adapting the N-200 for use in the

presence of varying levels of patient activity.

- The N-200 is equipped with two sets of default alarm limits, one for use in monitoring adults and one for neonates.

- Twelve hours of oxygen saturation and pulse rate data are stored in the trend memory, and one hour of saturation, pulse rate, and pulse perfusion data are stored in the event memory. These data can be provided to a variety of analog or digital output devices.

- Noninvasive NELLCOR sensors obtain measurements by optical means alone, using two light-emitting diodes as light sources. Specific sensors are available for use on neonates, infants, children, and adults.

- Patented automatic calibration mechanisms are incorporated in the N-200 (U.S. Patent 4,621,643 and others pending). The N-200 automatically calibrates itself each time it is turned on, at periodic intervals thereafter, and whenever a new sensor is connected. Instrument sensitivity changes automatically to accommodate a wide range of tissue thicknesses and skin pigmentations.

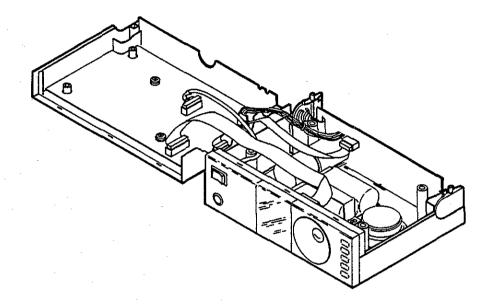

Internally, the monitor contains five printed circuit boards (PCBs), the battery, and a speaker. The largest circuit board (mounted on the top cover of the monitor) is the processor PCB, which contains the analog processing circuitry and the microprocessor with its associated circuitry. The power supply PCB is located on the back of the monitor. The battery charger PCB is located along the left side of the instrument chassis when viewed from the front. The display and driver PCBs are located immediately behind the front panel and contain the LED displays and front-panel switches.

The powerbase contains a power supply transformer, a mother PCB and three daughter PCBs. The mother PCB is mounted vertically at the front of the powerbase (facing the monitor); the daughter PCBs are mounted horizontally and mate to the mother PCB. Details of instrument assembly and disassembly are found in Section 4.

## **SECTION 3**

#### THEORY OF OPERATION

Theory of operation is presented in two parts. First, a general overview of the N-200's capabilities and the physical principles of its operation is presented. Next, the details of circuit operation are discussed.

## 3.1. GENERAL THEORY

The NELLCOR N-200 provides continuous, noninvasive, self-calibrated measurements of both functional oxygen saturation and pulse rate.

The instrument combines the principles of spectrophotometric oximetry and plethysmography. It consists of an electro-optical sensor that is applied to the patient and a microprocessor-based monitor that processes and displays the measurements. The electro-optical sensor contains two low-voltage, low-intensity light-emitting diodes (LEDs) as light sources and one photodiode as a light receiver. One LED emits red light (approximately 660 nm) and the other emits infrared light (approximately 920 nm).

When the light from the LEDs is transmitted through the tissue at the sensor site, a portion of the light is absorbed by skin, tissue, bone, and blood. The photodiode in the sensor measures the light that passes through, and this information is used to determine how much light was absorbed. The amount of absorption remains essentially constant during the diastolic (nonpulsatile) phase and is analogous to the reference measurement of a spectrophotometer.

With each heart beat, a pulse of oxygenated arterial blood flows to the sensor site. This oxygenated hemoglobin differs from deoxygenated hemoglobin in the amount of red and infrared light that it absorbs. The N-200 continuously measures absorption of both red and infrared light and uses those measurements to determine the percentage of functional hemoglobin that is saturated with oxygen.

When the pulsatile blood is present, the light absorption at both wavelengths is changed by the presence of that blood. The *NELLCOR* N-200 then corrects the measurements during the pulsatile flow for the amount of light absorbed at the initial measurements. The ratio of the corrected absorption at each wavelength is then used to calculate functional oxygen saturation.

#### 3.1.1. C-LOCK ECG Synchronization

When the N-200 is provided with ECG input, it is receiving two signals that independently reflect cardiac activity: one from the sensor and the other from the ECG. This enhances the performance of the instrument in the presence of patient movement, as discussed below.

There is a time delay between the electrical and mechanical activity of the heart. When an ECG QRS-complex is detected, a pulse will be detected at the sensor site a short time later. The length of this delay varies with the heart rate, the patient's physiology, and the location of the sensor. The N-200 measures this time delay, and, after a few pulse beats, calculates the average delay between the occurrence of the R-wave and the detection of the optical pulse by the sensor. This average delay is used to establish a "time window" during which the optical pulse is expected at the sensor site.

A pulse that is received within this time window is considered a real pulse and is processed. A pulse that is received outside the time window is considered an artifact and is rejected. Both the average delay and the time window are recalculated with each pulse beat to adjust for changes in the patient's physiology. If the ECG signal is irregular or noisy, then the optical pulse alone is used to determine pulse rate and initiate saturation calculations. Since artifacts often appear independently in the ECG and pulse signals, this method provides the most stable measurement of pulse rate and saturation.

If either the optical pulse or the ECG signal is markedly degraded or lost, the appropriate alarm activates and *C-LOCK* ECG synchronization is suspended. It will resume once both inputs have been re-established.

#### 3.1.2. Automatic Calibration

Patented automatic calibration mechanisms are incorporated into the N-200 pulse oximetry system (U.S. Patent 4,621,643 and others pending). Each sensor is calibrated when it is manufactured: the effective mean wavelength of the red LED is determined, coded into a calibration resistor, and then checked. That calibration resistor is read by the N-200 software to determine the calibration coefficients that are used for the measurements obtained by that sensor.

The N-200 is automatically calibrated each time it is turned on, at periodic intervals thereafter, and when a new sensor is connected. Also, the intensity of each LED in the sensor is adjusted automatically to compensate for differences in tissue thickness.

#### 3.1.3. Functional vs. Fractional Saturation

Because the N-200 measures functional oxygen saturation, it may produce measurements that differ from those of instruments that measure fractional oxygen saturation.

Functional oxygen saturation is defined as oxygenated hemoglobin expressed as a percentage of the hemoglobin that is capable of transporting oxygen. Because the N-200 uses two wavelengths to measure saturation, it measures only oxygenated and deoxygenated (i.e., functional) hemoglobin. It does not detect the presence of significant amounts of dysfunctional hemoglobin, such as carboxyhemoglobin or methemoglobin.

In contrast, some other laboratory instruments, such as the IL-282 CO-Oximeter, report fractional oxygen saturation values. Fractional saturation is defined as oxygenated hemoglobin expressed as a percentage of total hemoglobin, whether or not that hemoglobin is available for oxygen transport. Dysfunctional hemoglobin species are included in this calculation. Consequently, when measurements from the N-200 are compared with those from another instrument, it is important to consider whether the other instrument is measuring functional or fractional saturation.

#### 3.1.4. Measured vs. Calculated Saturation

When oxygen saturation is calculated from blood gas PaO2, the calculated value may differ from the oxygen saturation measurement of the N-200. This is because an oxygen saturation value that has been calculated from blood gas PaO2 has not necessarily been correctly adjusted for the effect of variables that shift the relationship between PaO2 and saturation. These variables include temperature, pH, PaCO2, 2,3-DPG, and the concentration of fetal hemoglobin. Refer to the Operator's Manual for additional information.

### 3.2. CIRCUIT-LEVEL DESCRIPTION

Refer to Section 9 for the instrument schematic and block diagrams. The major circuit sections consist of:

- the patient module

- the analog processing circuitry and microprocessor circuitry

- the front panel display logic

- the battery charger and power supply

- the instrument powerbase, which contains the data communications interface circuitry.

Since the measurement of oxygen saturation requires light of two different wavelengths, two LEDs (one IR and one red) are used to generate light, which is passed through the tissue at the sensor site into a single photodiode. The LEDs are illuminated alternately with a four-state clock. The photodiode signal, representing light from both LEDs in sequence, is amplified and then separated by a two-channel synchronous detector, one channel sensitive to the infrared light waveform and the other sensitive to the red light waveform. These signals are then filtered to remove the LED switching frequency as well as electrical or ambient noise, and then digitized by an analog to digital (A:D) converter. This digital signal is then processed by the microprocessor to identify individual pulses and compute the oxygen saturation from the ratio of the pulse seen by the red wavelength compared to the pulse seen by the IR wavelength.

Throughout this section and on the schematics, active low logic signals are designated by an overbar above the signal name (for example, "SIGNAL").

#### **3.3. PATIENT MODULE**

The patient module contains preamplifiers for the saturation (SAT) and electrocardiogram (ECG) signals (refer to SCHEMATIC PATIENT MODULE PCB). Power for the circuitry is  $\pm$  15 V generated by the processor board.

The drive current for the pair of sensor LEDs is supplied from the instrument, generated on the processor board (VIR and VRED on SCHEMATIC PROCESSOR PCB, SHEET 4). This waveform is a bipolar current drive which is passed through the patient module to the back-to-back sensor LEDs. A positive current pulse drives the IR LED and a negative current pulse drives the red LED. The drive current is controlled by a feedback loop on the processor board in response to photodetector response.

The detector photodiode generates a current proportional to the amount of light received. SAT preamplifier U2 is a current to voltage (I:V) converter in an inverting configuration that converts the DETECTOR current to a SAT voltage signal. The conversion ratio is 250 mV/ $\mu$ A. Voltage regulator VR1 biases the preamplifier to approximately +8.5 V output for 0 current input. This bias increases the swing of the I:V converter to an effective output swing of +8.5 V to -10 V. The additional voltage headroom is necessary for high ambient light conditions.

Instrumentation amplifier U1 preamplifies the ECG signal. Gain of the amplifier is set for approximately 30. Neon lamps DS1, DS2, and DS3 are used to protect U1 from potentially damaging high-energy pulses which may result from defibrillation procedures. Series resistors R1 and R2 provide further isolation from high transient currents. Diodes CR1 through CR4 shunt high-voltage transients to the low-impedance power supplies. Resistors R3 and R4 pull the input signal lines to the power supply voltage levels when an ECG signal lead has become detached.

Common mode signals A1 and A2 from U1 are summed through R9 and R10, amplified, and inverted through operational amplifier U2. The output of U2 is fed back to the patient to maintain the patient at a constant potential and eliminate common mode signals from the input sensing leads. The ECG signal from U1 goes directly to the processor board.

The sensor contains a calibration resistor that codes the wavelength of the red LED mounted in the sensor. Because the wavelength of the red LED varies from one sensor to another, an error would result in the computation for oxygen saturation if not corrected for by the calibration resistor. This calibration resistor is connected directly through the instrument cable assembly to the processor board. Since the patient module assembly is used close to the patient environment, it is potted in epoxy to prevent any damage from moisture and is not repairable. In the event of failure or damage to the sensor contacts or to the cable or connector itself, the entire assembly must be replaced.

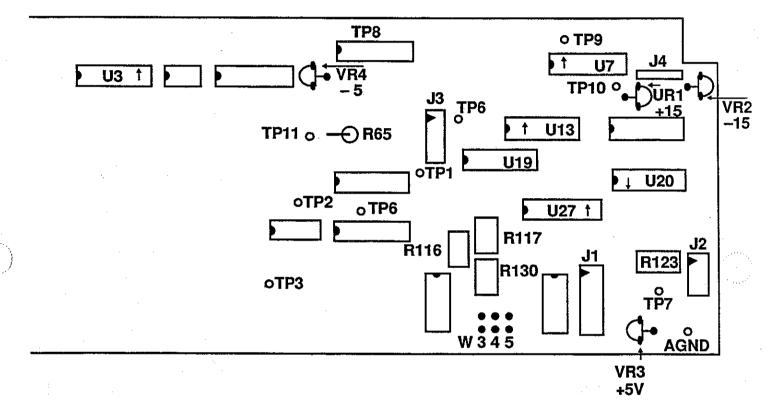

#### 3.4. PROCESSOR PCB

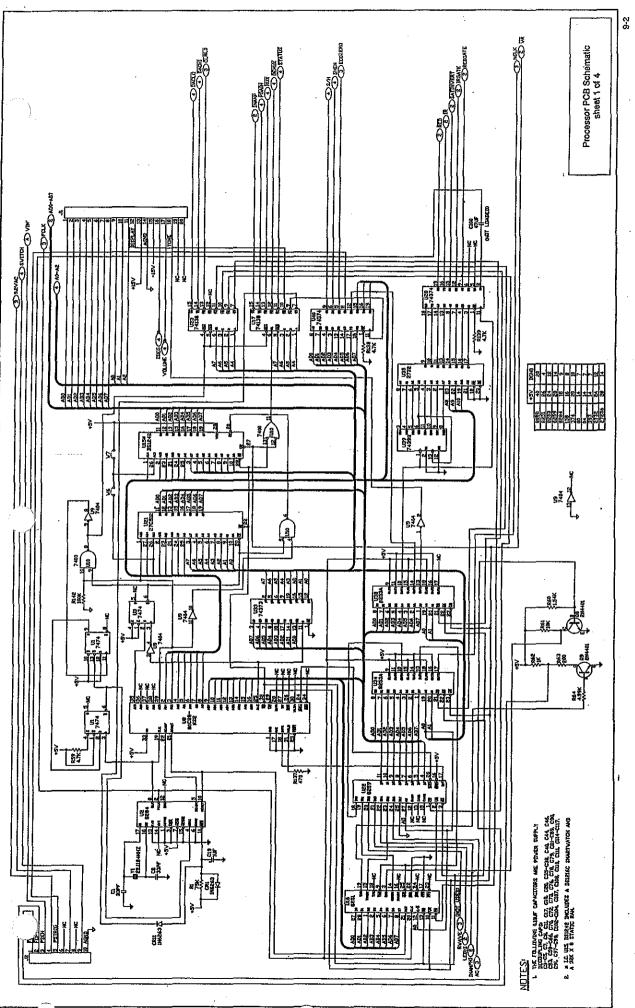

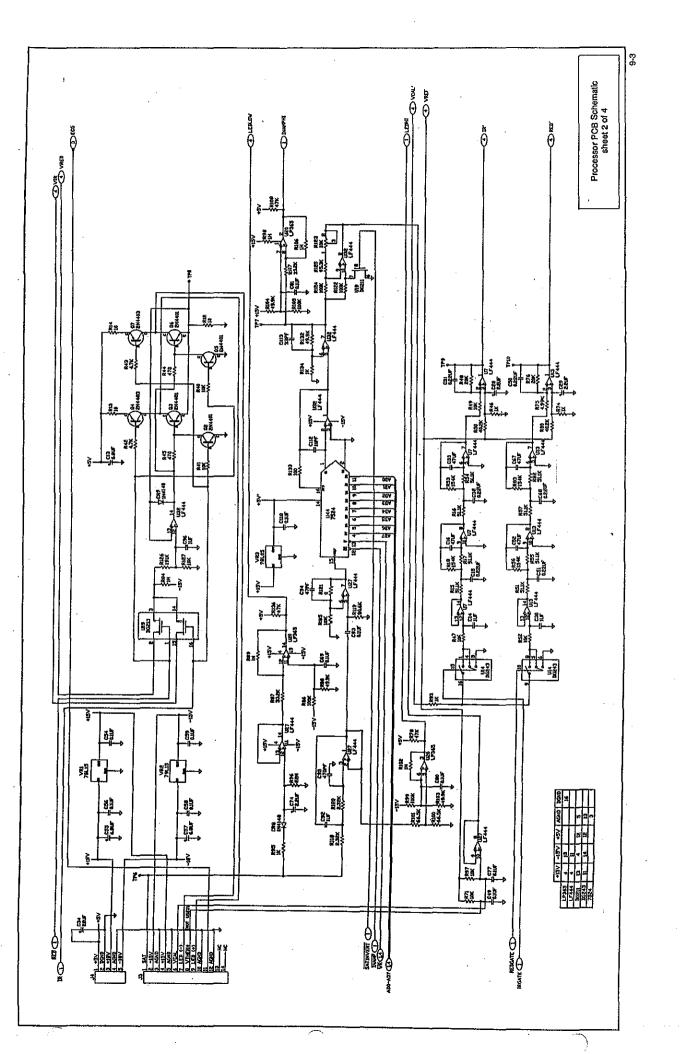

The processor PCB contains most of the active circuitry in the N- 200, both analog and digital. Refer to SCHEMATIC PROCESSOR PCB, SHEETS 1 through 4, in the following discussion.

#### 3.4.1. Digital Section

The digital section of the N-200 processor PCB is shown on SCHEMATIC PROCESSOR PCB, SHEET 1.

#### 3.4.1.1. Microprocessor Subsection

The processing power of the N-200 pulse oximeter is contained within a standard 8088 minimummode microprocessor RAM/ROM configuration. Program memory is contained in one 64K x 8 EPROM (U21) while the 32K x 8 system RAM (U15) provides a data buffer, stack, scratchpad, and trend and event data memory functions. The RAM is mated to a clock/calendar socket, which provides time and date information used during trend and event recording, as well as battery back-up to prevent data loss when the instrument is in standby.

Processor (U8) pins 9 through 16, designated AD0-AD7, are multiplexed to alternately present the low-order address byte and a data byte. On the first clock cycle of an instruction, an address is present on these lines. The ALE signal (U8, pin 25) pulses high to latch the lower byte of the address in transparent octal latch U33. In the following clock cycles, data can flow bidirectionally on these lines.

The upper 4 address lines of U8 (A16 through A19) are also multiplexed, alternately carrying address and status information. Only the uppermost bit (A19) is used in the N-200 for address decoding. This pin (U8, pin 35) is at logic high when the system is addressing ROM space, and low when it is addressing RAM or performing input/output (I/O) functions. The processor's ALE signal latches this bit in flip-flop U3.

### 3.4.1.2. Memory Map

The entire processor system is memory mapped. That is, all devices on the 8088 data bus are accessed (read from or written to) at specific memory locations in the 1 Mbyte memory range. The upper 512 kbytes of memory are considered ROM space; the lower 512 kbytes are considered RAM and I/O space. ROM resides in the top 64 kbytes of memory, with the program starting at hex FFFF0 after reset. Since only 64 kbytes of the ROM space are actually used, images of the 64 kbyte ROM are repeated up to the 512 kbyte limit because memory is not uniquely decoded.

RAM begins at address 0 and extends for 32 kbytes. I/O functions reside directly above RAM, starting at address hex 8000. The I/O select lines coming from U17 and U23 are 16 addresses apart, ranging from hex 8000 to hex 80F0.

#### 3.4.1.3. Walt State Generator

Two D-type flip-flops in U1 form a wait-state generator. A wait state of one clock cycle is generated whenever I/O is addressed (that is, whenever a peripheral device is accessed). Accessing RAM (addresses between 0 and 32k) generates no wait state.

### 3.4.1.4. Clock Generator

U2 produces a processor clock with the correct duty cycle, as well as a peripheral clock which drives UART U16 and the two timer chips U34 and U38. Because the 8088 processor U8 requires a 33% duty cycle clock, the crystal oscillator runs at 22.1184 MHz, three times the desired frequency. U2 divides the 22.1184 MHz signal by three and provides the correct duty cycle to U8.

A reset circuit composed of R1, CR1, and C19 ensure that U2, pin 11, is held low immediately following power-up. This maintains the logic at a known state while the power supplies and crystal oscillator stabilize.

#### 3.4.1.5. Timer Circuits and UART

Additional peripheral devices include two 82C53 triple counter/timer chips U34 and U38 and UART device U16. The 82C53 sections control:

- 1. Display update interrupts to the 8088 at a 2.5 ms rate (also provides for real time references within the system program).

- 2. Baud rate for the 8251 UART (U16), which drives an optical data link for communication between the monitor and powerbase. The baud rate is set at 19.2 kbaud.

- 3. Audio frequency generation for the alarm beeper (TONE).

- 4. Clock frequency for the ECG switched-capacitor notch filter (NCLK).

- 5. Pattern generator clock frequency (the pattern generator is composed of U39, U35, and U28), which controls synchronous circuit operations.

## 3.4.1.6. Pattern Generator

The pattern generator (U39, U35, and U28) provides software selectable timing patterns used to control sync detector gating, LED control, and power supply synchronization triggers.

In operation, a preprogrammed bit pattern in EPROM U35 is continuously cycled through by counter U39, clocked by the divided down processor clock output. One of eight patterns can be selected through address lines A8-A10 on U35 through octal latch U40. Additional latch U28 serves to "de-glitch" the EPROM outputs by holding the last output byte while the counter steps to the next address. Various patterns within the EPROM are used to select LED/sync detector sampling speeds along with real time calibration patterns and diagnostic timing.

## 3.4.2. Analog Front End and LED Current Drive

The analog circuitry and LED drive circuitry is shown on SCHEMATIC PROCESSOR PCB SHEET 2.

#### 3.4.2.1. Main Analog Signal Flow

The SAT signal from the patient module passes through a 50 kHz low-pass filter (one quarter of quad operational amplifier U27 in a 2-pole Butterworth configuration). The signal is then AC coupled to another U27 op amp, configured as a gain stage with unity gain. A variable attenuator composed of Digital-to-Analog Converter (DAC) U44 and amplifier U32 is followed by a noninverting amplifier (U32) with gain of 51. Together, the two circuits provide a programmable variable-gain function that can vary between 0 and 51. This gain is called INAMP (input amplifier) gain. In operation, the composite signal is always maximized by the operating software such that the targest possible signal is fed into the next stage of synchronous demodulation; this helps optimize the signal/noise (S/N) ratio.

Voltage regulator VR3 provides a low-noise 5 V DC supply for U44.

#### 3.4.2.2. Sync Detector

The INAMP stage drives sync detector U32. If the SATINVERT signal is at logic low, U32, pin 10, is pulled to ground potential, and the stage becomes an inverting amplifier with unity gain. When SATINVERT is high, the stage becomes a noninverting voltage tollower. Trimpot R123 is used to equalize the magnitudes of the inverting and noninverting gains.

#### 3.4.2.3. Demultiplexer

The output of the sync detector drives both halves of U14. U14 demultiplexes the signal synchronously with the IRGATE and REDGATE steering pulses. Low-pass filters (R47 and C14; R52 and C30) suppress switching transients. The signal in each channel is then buffered by a unity-gain amplifier and low-pass filtered by two active-filter stages (each with two poles at approximately 20 Hz). The filters are slightly overdamped to improve step response.

The last stage in each channel is an offset amplifier with gain, which offsets the signals by a small positive voltage (approximately 0.25 V). This voltage is derived from VREF (set at 10 V) and the voltage dividers R50 and R46 (R80 and R74). Since the Analog-to-Digital Converter can only process 0 to 10 V signals, the positive bias provides a reference floor for analog-to-digital conversion stages that follow to ensure that the total chain offset errors of the op amps can never drive the outputs negative. Because the RED channel has twice the gain of the IR channel, the offset seen at TP10 is twice that seen at TP9 when no signal input is present.

### 3.4.2.4. Logic Flags

Several flags are produced in the analog section of the processor PCB that instruct the processor to vary circuit parameters (gain and LED drive currents) so that signal levels are kept safely below those which would saturate on-board electronics.

- LEDHI The SAT signal coming from the patient module can range from +8.5 V to -10 V without saturating the patient module's analog amplifiers. Comparator U20 compares the filtered (and halved) SAT signal to a -5 V reference. When the signal drops too low (SAT less than -10 V), the signal is too close to the patient module's negative power rail. This condition sets the LEDHI flag, which interrupts the processor. The processor then reduces the LED drive currents to avoid signal saturation.

- INAMPHI Following the INAMP programmable gain section, another comparator (U20) generates the INAMPHI interrupt. This circuit compares the signal to a 10 V reference. When the INAMP gain is set too high, the signal level exceeds 10 V, and the INAMPHI flag is set. The processor then reduces the gain of the INAMP stage to lower the signal level.

- LEDLOW If a sensor is exposed to bright light, the output of the patient module is driven negative an amount proportional to the ambient light exposure. This condition occurs because the ambient light causes an increase in the photodetector current from the sensor. The I:V converter in the patient module converts the increased current to a negative voltage.

When comparator U20 senses negative-going voltage signals more positive than its -5 V reference, it sets LEDLOW high. The processor polls the LEDLOW flag and increases drive current to the LEDs when LEDLOW is high for improved S/N ratio. This condition occurs when the patient removes the sensor from high ambient light exposure. A delay of up to 30 seconds is provided to prevent the LED current from changing in frequently changing ambient light conditions. The delay is implemented by passing the SAT signal through a fast-attack/slow-decay circuit formed by R95, R96, C74, CR8, and U27 before it reaches comparator U20. The orientation of diode CR8 causes the circuit to be sensitive only to negative-going signals.

#### 3.4.2.5. LED Drive Circuitry

The analog switches in U19 allow the gating of separate drive voltages (VRED and VIR) for the red and IR LEDs so that the two LEDs can be run at different intensities. VRED and VIR are determined by the SAT signal level from the photodetector/patient module and set by the sample/ hold subsection (SCHEMATIC PROCESSOR PCB SHEET 4, U18 and U11) on the processor board. Control signals RED and IR come from the pattern generator (SCHEMATIC PROCESSOR PCB SHEET 1, U28). Drive circuitry converts the VRED and VIR voltages to drive currents.

The voltage level at TP8 is translated to current for LED drive via a bridge driver circuit consisting of error amplifier U32 and the six signal transistors Q2 through Q7. The bridge output (J3 pins 7 and 9) goes to the back-to-back IR/red LEDs of the sensor assembly. In operation, the signals RED and IR select IR or red LED drive, determining the half of the bridge circuit that is active and forward biasing either the red or IR LED; Q3 and Q6 act as current boosters for U32, while Q2, Q4, Q5, and Q7 steer the current flow. The current through the LEDs is sensed by resistor R12 and fed back to pin 13 of error amp U32, thus maintaining a constant current proportional to voltage at TP8 and independent of the +5 V supply that powers the bridge. Maximum LED current is approximately 50 mA.

3-7

#### 3.4.3. ECG Front End

Refer to SCHEMATIC PROCESSOR PCB SHEET 3 in the following discussion.

#### 3.4.3.1. Active Filters

The ECG signal from the patient module is conditioned by 5 stages of active filtering. The total gain of the chain of active filters is approximately 32.

The ECG is first low-pass filtered by U12 and associated circuitry. The two filter poles are set at 40 Hz and the gain is equal to 1.

U6 is a switched-capacitor notch filter with a gain of 0.32. Capacitor switching frequency (NCLK) is derived from timer IC U34 (PROCESSOR PCB SHEET 1), and is set by the processor to remove AC power line interference. (See Section 3.4.3.4., Power Line Frequency Sensing.)

A second 2-pole, 40-Hz low-pass filter follows the notch filter. This filter removes the switching transients inherent in switched capacitor filter U6.

A high-pass filter (U12) with gain of 101 and cutoff frequency 0.5 Hz follows the second low-pass stage. Because this filter stage has a long time constant, a processor control input (ECGZERO) resets the filter by discharging the filter capacitors. Reset occurs under the following conditions: if a lead comes loose from the patient (or the ECG signal is contaminated by patient muscle contractions), the ECG signal baseline can be driven into a railed condition. This occurs because of the high (approximately 1000) combined gain of the patient module and ECG front end filters. When the ECG baseline rises too much, the processor temporarily brings ECGZERO low to reset the filter.

#### 3.4.3.2. Offset Amplifier

An offset amplifier (U12) biases the filtered ECG signal by +5 V so that the A:D converter can digitize the entire waveform (the A:D converter can only process positive analog signals). The output of the offset amplifier (ECG') is digitized by the A:D converter and provided as a data output by the powerbase.

#### 3.4.3.3. Detached Lead Indicator

A 3-stage circuit composed of absolute-value amplifier U5, voltage comparator U4, and D-type flip-flop U3 generates the LEADOFF flag. The circuit examines the condition of the ECG signal at the input to the switched-capacitor notch filter U6, after it has undergone one stage of lowpass filtering.

A detached lead is sensed as follows: within the patient module, a biasing resistor network drives the ECG signal to one of the supply rails ( $\pm$ 15 V) if one or both ECG signal leads becomes detached from the patient. If the signal is driven to the negative supply rail, it is converted to a positive voltage by absolute value amplifier U5. The output of this circuit is compared to a 10 V reference by comparator U4. A voltage in excess of 10 V drives the output of U4 low, setting and latching flip-flop U3 through NAND gate U10. When the flip-flop has latched, the LEADOFF logic signal is set high, notifying the processor that a lead has come loose. When the processor polls LEADOFF and discovers that it is at a logic high, it stops using the ECG R-wave as a gating mechanism and lights an LED on the instrument front panel to notify the user that the ECG signal has been lost. The processor clears the flip-flop with CLRLO after a high LEADOFF signal has been recognized. NAND gate U10 is provided to latch the flip-flop during brief (intermittent) lead-off conditions.

#### 3.4.3.4. Power Line Frequency Sensing

The mains power AC signal going into the power supply board is transformed to 9.2 VRMS and sensed by one-volt-crossing comparator U20. The one-volt-crossing detector produces the logic signal AC, which interrupts the processor at the frequency of the AC power line. This signal is used to set notch filter U6 to the line frequency, automatically adjusting for 60 Hz or 50 Hz power.

#### 3.4.4. A:D/D:A Subsection

The A:D/D:A subsection is shown on SCHEMATIC PROCESSOR PCB SHEET 4.

The A:D/D:A subsection performs both analog to digital and digital to analog conversions. A unique feature of the design is the ability to subtract variable DC offsets and post-amplify signals prior to A:D conversion. This allows for accurate measurements of small modulation levels on large DC levels without slow-response AC coupling.

#### 3.4.4.1. A:D Conversion

The sequence of a typical A:D conversion routine is as follows:

- A) The 8088 processor selects an analog channel for conversion by writing to 8-to-1 analog multiplexer U24. Signals available for conversion are:

- 1R' the demultiplexed and filtered IR detector channel signal

- RED' the demultiplexed and filtered RED detector channel signal

- ECG' the filtered ECG waveform

- VCAL' the filtered voltage from the calibration resistor within the sensor

- VPS the power supply voltage, used to determine whether the system is running on AC power or batteries and to check the battery voltage when the instrument is operating on battery power

- ISEG a voltage level from the display driver board, used to detect bad segments or light bars on the display during power-up test

- VREF approximately 10 V reference voltage used for board alignment

- GROUND analog ground potential used for board alignment.

- B) Set programmable amplifier U30 gain by writing to latch U42.

- C) Set desired analog offset value to be subtracted at U25, pin 2, by writing two bytes (low byte, high nybble) to 12-bit bus-compatible DAC U43 (12 bits, 0-10 V).

- D) Now a scaled analog value is present at the output of programmable gain amplifier stage U37, pin 1, (TP3). The offset voltage has been subtracted by differential amplifier U25 and amplified by programmable amplifier U30 and U37. The total range of programmable gain is 1/8 to 16.

- E) Triggering the sample and hold line (S/H) causes U36 to hold the scaled voltage for A:D conversion.

- F) The 8088 processor begins executing a successive approximation routine (SAR).

- G) The SAR performs a binary search sequence by setting up a voltage on the D:A converter U43 which is compared to the held signal voltage via comparator U29. The result of this comparison is polled by the processor via buffer U41.

- H) The SAR continues until the least significant bit has been set. Each 12-bit conversion is accomplished in approximately 100 µs.

#### 3.4.4.2. D:A Conversion

The analog sample/hold circuits formed by analog demultiplexer U18 and quad operational amplifier U11 are used to update and store the following four analog signals:

- VIR, which controls the IR LED brightness

- VRED, which controls the red LED brightness

- VOLUME, which controls the speaker volume.

- RWTHRESHOLD, not used.

In operation, the processor sets up an analog voltage on analog demultiplexer U18, pin 9, by writing to DAC U43. U18 is enabled through U18, pin 3, and the processor selects which output is written with address lines A0 through A2. When U18 is enabled, the voltage at U18, pin 9, is routed to one of the four outputs S1 through S4, charging storage capacitor C39, C41, C42, or C43. When U18 is disabled, the capacitor voltage is held by the very low leakage follower op amp U11 until the next update.

#### 3.4.5. Timing and Control

Most processor timing and control flags are generated in circuits shown on SCHEMATIC PROCESSOR PCB SHEET 2 and 3. Processor timing is affected by two types of logic flags:

- Polled processor I/O signals

- Processor interrupts, which may occur asynchronously.

Many of these flags are discussed elsewhere in this section and all are summarized below.

#### 3.4.5.1. Polled Processor Flags

Buffer U41 allows the 8088 processor to poll the following logic flags:

SWITCH indicates the state of the front panel switch (logic low indicates ON position)

3–10

LEADOFF indicates that an ECG lead has become detached, and that the ECG signal from the patient module was near saturation level as a result

LEDLOW indicates that LED drive currents should be increased to increase SAT S/N ratio

DACMP the output of voltage comparator U29, used in SAR A:D conversion

Four jumpers W2, W3, W4, W5, which are selectively installed to place the processor in various diagnostic modes.

#### 3.4.5.2. Interrupt Processor Flags

- AC interrupts the processor at the frequency of the AC power line

- LEDHI instructs the processor to decrease the LED drive currents in the presence of ambient light to avoid SAT signal saturation

- INAMPHI indicates that the INAMP gain is set too high. The processor then reduces the gain of the INAMP stage to lower the signal level to avoid saturation

- TxRDY signals that UART U16 is ready to transmit another character

- RxRDY signals that UART U16 has received a new character

- INT real-time interrupt from interrupt controller U22

#### 3.5. FRONT PANEL DISPLAY

Front panel display is accomplished by two circuit boards:

- Driver PCB, which contains drive circuitry for the display LEDs

- Display PCB, which contains the display LEDs and pushbuttons.

#### 3.5.1. Driver PCB

The driver circuit board is shown on SCHEMATIC DRIVER PCB. Refer to this schematic in the following discussion.

During power-up, CR2, R10, and C11 provide a short-duration reset pulse to all latches on the driver board. This reset pulse clears all front-panel display elements.

Two different mechanisms are used to drive the display:

- digit and bargraph drivers

- drivers for the lightbars used with other front-panel indicators such as "PULSE SEARCH" and "AUDIO ALARM OFF."

#### 3.5.1.1. Digit and Bargraph Drivers

A total of 8 components comprise the digit and bargraph displays (DIGIT 0 through DIGIT 5, BARGRAPH 0 and BARGRAPH 1). The drive signals for these displays are multiplexed.

Latch U12 and decoder U13 are used to select which digit or bargraph to update. Latch U10 and driver U11 determine which segments within the selected digit or bargraph are illuminated.

#### 3.5.1.2. Lightbar Drivers

The lightbars are driven by latch circuitry and are not multiplexed. U3 and U8 drive lightbars with the following signals:

DP lights decimal point in the 7-segment digital displays

ALMINH lights AUDIO ALARM OFF lightbar

N/C not connected

PLSSRCHLO with PLSSRCHHI, lights PULSE SEARCH lightbar

PLSSRCHHI with PLSSRCHLO, lights PULSE SEARCH lightbar

LOWSAT lights LOW SAT lightbar.

U2 and U9 drive the remaining lightbars with the following signals:

HISAT lights HIGH SAT lightbar

LOWRATE lights LOW RATE lightbar

HIRATE lights HIGH RATE lightbar

BATLO lights LOW BATT lightbar

BATON lights BATT IN USE lightbar

ECGLOST lights ECG LOST lightbar

ECGON - lights ECG IN USE lightbar

Decoder U6 takes the select line from the processor (DISPLAY) and the three low address lines from the processor (A0, A1, and A2) and uses them to select a latch for display updating.

#### 3.5.1.3. Front Panel Controls

Decoder U6 also lets the processor select octal buffer U1, which reads the state of inputs BUTTON 0 through BUTTON 4 and control knob rotation information relayed through UP/DOWN (U/D) counter U5.

The control knob consists of a two channel optical chopper, with the two channels mechanically 90 degrees out of phase to each other, and a dual channel optical slot detector. Schmitt trigger inverters U4 are used to clean up the signals from the knob, one inverter per channel. Channel A provides the clocking pulse for U/D counter U5; Channel B provides the direction (U/D) signal.

The phase relationship between the two channels provides an UP or DOWN count command to the counter, depending on which way the knob is turned (clockwise rotation results in count-up commands).

To detect a change in the U/D counter, the processor reads the twos-complement value of the counter's output and adds it to its accumulated turns count. After it accumulates the counter value, the processor generates a signal into the LOAD line of U5 to clear it for the next count value.

#### 3.5.1.4. Power-Up Display Element Test

Differential amplifier U7 senses the power return line of driver ICs U8, U9, and U11 by monitoring the voltage across resistor R9. The sensed voltage is proportional to the current flowing through the driver ICs. The voltage is amplified with a gain of 10 and is provided to the A:D converter as signal ISEG (PROCESSOR PCB SHEET 4, U24). The processor digitizes ISEG and uses it during the power-up display test to determine whether any display element has a shorted or open LED segment.

#### 3.5.1.5. Speaker Driver Circuit

The sample/hold VOLUME signal from the processor (SCHEMATIC PROCESSOR PCB SHEET 4, U11) controls the amount of current going into the speaker's SPEAKER(+) lead. The TONE signal (SCHEMATIC PROCESSOR PCB SHEET 1, U38 and U9) switches FET Q2 to alternately connect or disconnect the SPEAKER(-) lead from ground. The frequency of the TONE signal determines the pitch of the sound produced. The harsh-sounding square wave of TONE is softened by filter capacitor C6. Diode CR1 suppresses transients from the inductive speaker load. Transistor Q1 supplies a current boost for the U7 operational amplifier.

#### 3.5.2. Display PCB

The display circuit board is located immediately behind the front panel and contains the numeric LEDs, the LED indicator lamps, the control buttons and the control knob, as well as associated current limiting and pull-up resistors.

## 3.6. POWER SUPPLY PCB

The power supply circuitry is shown on the SCHEMATIC POWER SUPPLY PCB drawing.

The power supply board contains two switching power supplies in flyback converter configuration. The supplies are capable of providing 2 A at +5 V, 100 mA at +18 V, and 100 mA at -18 V.

Pulse width modulator (PWM) U2 controls the +5 V supply; PWM U4 controls the +18/-18 V supply. The PWMs sense the DC output voltages through their INV (pin 1) inputs and control the pulse width at the gates of switching FETs Q2/Q4 and Q3. Voltage regulator VR1 provides 5 V power and a 5 V reference to the two PWMs. Schmitt inverters U3 provide low impedance active current drive to the somewhat capacitive gates of the FET switching transistors, minimizing drain rise and fall times.

Also resident on the power supply board is one half (monitor side) of the powerbase-monitor optical link, formed by diode DS1 and phototransistor Q1.

## 3.7. BATTERY CHARGER PCB

The battery charger PCB is shown on the SCHEMATIC BATTERY CHARGER PCB drawing. The battery charger PCB contains two major circuits:

ON/STDBY control circuitry

Battery charger circuitry

#### 3.7.1. ON/STDBY Control Circuit

The ON/STDBY control circuit is shown on the bottom portion of the schematic.

The ON/STDBY switch J1 is shown in the ON position. It does not switch power. Rather, it provides a logic control signal (SWITCH) that is polled by the main processor through a tri-state buffer (U41 on SCHEMATIC PROCESSOR PCB SHEET 4). When the processor senses a change in switch position from ON to STDBY through this signal, it executes a shutdown procedure. The ON mode is activated by bringing the gate of FET switch Q1 high, which provides a low impedance connection between power supply ground (labeled "P") and signal ground. STDBY mode is activated by cutting off Q1. Power supply voltage, VPS, may be either the battery voltage or the rectified and filtered AC voltage from the powerbase, depending on the mode of operation.

In the following sections, the circuit is examined as the ON/STDBY switch is moved first from ON to STDBY, and then as the instrument is returned to the ON state.

#### 3.7.1.1. ON State

In the ON state, capacitor C2 is discharged. The combination of R5 and C2 forms a watchdog timer that ensures processor control over instrument power. If C2 is allowed to recharge, pin 8 of U1 will go low, flip-flop U2 will be cleared, the gate of Q1 will go low, and the connection between power and signal grounds will be broken.

The processor keeps C2 from recharging by placing a negative pulse on the power supply enable line (PSEN) at least once every 150 ms. The pulse is AC-coupled through capacitor C1, its rising edge producing a narrow positive-going pulse on U1, pins 1 and 2. The resulting low pulse on U1, pin 3 periodically discharges C2 through diode CR4. Capacitor C1 ensures that only active transitions on PSEN, not static highs or lows, have an affect on the watchdog timer. The N-200 is thus placed in the STDBY state if an abnormal condition "hangs" the processor.

#### 3.7.1.2. ON to STDBY

The ON to STDBY transition can occur either by placing switch J1 in position 1 (STDBY), or in response to a decline in battery voltage below approximately 5.6 V.

Placing J1 in the STDBY position causes the voltage on the polled SWITCH signal to rise. If this occurs, or if battery voltage falls below 5.6 V, the processor blanks the front-panel displays and executes an infinite loop routine that does not involve pulsing PSEN. As a result, watchdog timer capacitor C2 is not discharged, U1, pin 9, voltage rises, U1, pin 8, voltage falls, and flip-flop U2 is cleared. The resulting logic low at U2, pin 5, shuts off FET Q1, placing the instrument in the STDBY state.

#### 3.7.1.3. STDBY State

With the front panel switch in the STDBY state, VPS charges capacitor C5, and the SWITCH signal is maintained at logic high. SWITCH voltage is clamped to logic levels by protection zener diode CR8. Zeners CR1 and CR3 perform similar functions elsewhere in the circuit.

In STDBY, capacitor C2 is charged to 5 V through resistor R5.

## 3.7.1.4. STDBY to ON State

When the switch is moved to the ON position, C5 discharges through R7 and provides a momentary positive voltage pulse to Schmitt NAND gate U1, pins 4 and 5. In response, U1, pin 6, falls to logic low, discharging capacitor C2 through diode CR5, and setting D-type flip-flop U2. When the flip-flop is set, U2, pin 5, goes to logic high, placing positive voltage on the gate of FET switch Q1. Positive gate voltage on Q1 creates a low-resistance path between signal ground and power ground. As the switched voltage pulse from C5 discharges through R7, U1, pin 6, returns to a logic high, and C2 (the watchdog timer) begins recharging. The processor again begins to periodically discharge C2 to maintain the instrument in the ON state.

#### 3.7.1.5. Voltage Regulator

Micropower voltage regulator U3 provides 5 V power to the battery charger PCB. Battery charger and ON/STDBY sensing circuitry is always on as long as the battery maintains sufficient voltage. Total current drain for the circuits on this board is approximately 40  $\mu$ A.

#### 3.7.1.6. Power-On Time Delay

A time delay provided by CR2, R6, and C3 at the gate of Q1 allows the power supplies to return to ground potential on occasions when the switch is cycled rapidly. Without this time delay, cycling the switch from ON to STDBY and back to ON might not allow the power supply voltage to fall far enough to generate a reliable power-up reset pulse to the processor (SCHEMATIC PROCESSOR PCB, SHEET 1, power-up reset circuit R1, CR1, and C19).

#### 3.7.2. Battery Charger Circuit

Battery charger circuitry is shown in the upper part of the schematic.

AC power VCB+ and VCB- (12.5 VRMS) is taken from one of the power supply transformer secondary windings. It is rectified through diode bridge CR6 and filtered by C7 to provide a positive voltage for voltage regulator VR1. Current sensing resistor R15 provides current limiting through Q2 and Q3, cutting output voltage when current draw increases above 375 mA. Trimmer potentiometer R12 adjusts the nominal battery charging voltage to 7.1 V at TP5.

Diode CR9 prevents back-discharge through the regulating circuit when AC power is removed. With AC power disconnected, battery voltage can vary between 6.6 V and 5.6 V.

#### 3.8. POWERBASE

The powerbase contains electronics for data communications for the N-200. It is composed of a mother PCB and three daughter PCBs.

#### 3.8.1. Mother PCB

The mother board is shown in the SCHEMATIC MOTHER PCB POWERBASE.

The mother board provides power for the rest of the powerbase electronics. Bridge rectifier U2 charges filter capacitor C1. The AC voltage supplied at AC( $\pm$ ) is typically 7.5 V RMS. Voltage regulator U3 and current booster Q1 form a linear regulator that lowers the rectified AC voltage to  $\pm$ 5 V.

Portions of the powerbase analog circuitry require  $\pm 15$  V power. DC:DC converter U1 derives these voltages from the +5 V supply. U4 and U5 regulate these voltages down to  $\pm 12$  V for use in the RS232 serial port.

Diode CR1 and phototransistor Q2 form one half (powerbase side) of the powerbase-monitor optical link.

#### 3.8.2. Upper and Lower Daughter PCBs

The upper and lower daughter PCBs comprise the digital portion of the powerbase electronics.

#### 3.8.2.1. Upper Daughter PCB

In the upper daughter PCB, 8085 processor U5 is driven by a 6.144 MHz crystal. A watchdog timer comprised of U6, C7, CR1, R5, Q1, R6, and C8 monitors the Serial Output Data (SOD) signal from U5, pin 4. If SOD does not produce a positive pulse within any 100 ms period, the watchdog timer sets the trap pin (U5, pin 6) which causes the 8085 to reset to address 0. Delay circuit CR2, R9, and C10 provides reset on power up.

Addresses presented on the multiplexed address/data bus of U5 are held by latch U2 when ALE (U5, pin 30) pulses high. 16-kbyte EPROM U4 is mapped starting at address 0, and 8-kbyte RAM U3 is mapped starting at HEX 4000. I/O for the upper daughter PCB is memory-mapped. Addresses are decoded on the lower daughter PCB.

Buffer U1 reads several digital signals:

Four switches S1 through S4:

----S1 and S2 (ZERO and FULL) set zero and full-scale on all analog outputs

-S3 (TREND) initiates a TREND printout

-S4 (EVENT) initiates an EVENT printout

- Jumpers W1 and W2, which, when installed, place the system in various diagnostic modes

- SCALE, which is the output of switch SW1 (SCHEMATIC MIDDLE DAUGHTER PCB POWERBASE), sets the SAT analog output range (0-100% or 50-100%)

- ECGTRIG, which is generated with every R-wave when an external ECG monitor is used (SCHEMATIC MIDDLE DAUGHTER PCB POWERBASE, U7, pin 7).

#### 3.8.2.2. Lower Daughter PCB

U6 and U7 provide address decoding for all devices in the powerbase. I/O functions begin at HEX 8000.

Timer circuit U4 generates the real-time interrupt RST7.5 (U4, pin 10). U4 also produces the baud rates for UARTs U2 and U5. U5 drives the powerbase side of the monitor-powerbase optical link at 19.2 kbaud. Circuit elements associated with U5 provide signal conditioning for transmitting and receiving on the optical communication link. The link's LED and phototransistor are shown on the SCHEMATIC MOTHER PCB POWERBASE drawing.

U5, pin 23 (RTS) is set low in software when the instrument is in an alarm condition, producing a logic high on U8, pin 11 (ALMOUT).

UART U2 drives the external RS232 interface and the fiber-optic output CR1. Level translator U3 performs the voltage level shift required for the TTL-RS232 interface. RxRDY (U2, pin 14) is returned to the main processor as RST5.5. Baud rates for both UARTs are derived from timer U4 (pins 13 and 17).

Buffer U1 reads 8-bit DIP switch S1, which is used to select the baud rate and data transmission format.

Connector J8 is a 9-pin miniature D type for the RS232 data link.

#### 3.8.3. Middle Daughter PCB

The middle daughter board (shown on SCHEMATIC MIDDLE DAUGHTER PCB POWERBASE) contains all of the analog circuitry for the powerbase. For purposes of discussion, the board can be divided into two portions:

- the sample/hold circuit, with its associated DAC and analog demultiplexer

- the ECG input circuit with self-adjusting threshold. This circuit triggers processor U5 on the upper daughter board whenever an external ECG signal appears

#### 3.8.3.1. Sample/Hold Circuit

Bus-compatible 8-bit DAC U5 is provided with a reference voltage of approximately -10 V by negative voltage regulator U6. Potentiometer R11 trims the output voltage of U1, pin 6, to  $+10.00 \pm 0.02$  V when DAC gain is set to maximum (the U1-U5 combination inverts the reference voltage). Switch SW1 selects a full scale analog output voltage of 1 V or 10 V by switching in the voltage divider formed by R2, R5, and R6.

U4 is a 1-to-8 bus-compatible analog demultiplexer. DAC output at U4, pin 9, feeds through to the selected output: U4 pin 5, 6, 7, or 8. Each output drives a separate sample/hold circuit made up of storage capacitors C4 through C7 and FET-input operational amplifiers U2 and U3. Zener diodes at the outputs of the sample/hold amplifiers protect against external short-lived transients. The 1 kohm output resistors guell oscillations which may occur when driving highly capacitive loads.

### 3.8.3.2. ECG Output

The ECG sample/hold channel is bidirectional. It differs from the other three channels in that the output signal is AC coupled (at a corner frequency of 0.5 Hz) to unity-gain buffer U2. Resistor R12 buffers the output of the unity-gain buffer when signals enter the ECG bidirectional port (J3). Incoming ECG signals are AC coupled through C16 and R25 to two parallel circuits:

- unity-gain buffer U3

- a peak follower circuit (composed of U2, CR9, C17, R27, and U3) with slow decay that stores the peak value of the R-wave from one peak to the next.

The peak follower circuit provides an adjustable threshold for sensing each ECG R-wave peak. Voltage comparator U7 produces a positive voltage pulse (ECGTRIG) when the ECG input signal exceeds the adjustable threshold determined by previous peak R-wave values.

## **SECTION 4**

#### TROUBLESHOOTING AND ASSEMBLY GUIDE

This section first discusses some potential difficulties, their possible causes, and suggestions for resolving them that do not require disassembly of the instrument. If the difficulty persists after following these suggestions, proceed to the subsections on detailed troubleshooting and disassembly. Refer if necessary to Section 5, Testing and Calibration. If qualified service personnel are not available, contact Nellcor's Technical Service Department at 1–800–NELLCOR or 415 887-5858.

NOTE: Instrument must be operating on AC power for the powerbase to be functional.

NOTE: To reset the powerbase microprocessor, disconnect and reconnect AC power.

#### **4.1. INITIAL TROUBLESHOOTING PROCEDURES**

- 1. The instrument does not turn on.

- The AC power is not connected and the battery is discharged. Connect to AC power. If the problem persists, check the AC fuse. If this does not resolve the problem, contact qualified service personnel or Nellcor's Technical Service Department.

- 2. The instrument operates on AC power but not on the battery.

- The battery is discharged. Fourteen hours are required to completely recharge the battery.

- The battery pack is defective or the battery fuse is open. Contact qualified service personnel or Nellcor's Technical Service Department.

- The battery charger is defective. Contact qualified service personnel or Nellcor's Technical Services Department.

- 3. The instrument operates on AC power, but the BATT IN USE indicator is always on.

- The powerbase is disconnected from the monitor.

- The instrument is not receiving AC power because the power cord is defective, is not connected, or is connected to a defective AC outlet. Replace the power cord, connect to AC power, or try another AC outlet.

- The AC fuse on the rear panel is defective. Replace the fuse (see Section 4.4.1.).

- 4. The instrument displays an error message.

- "Err 1" indicates defective RAM (data memory). See Section 3.4.1.1.

- "Err 2" indicates defective ROM (program memory). See Section 3.4.1.1.

- "Err 3" indicates a damaged display or indicator. See Sections 4.3.4. and 3.5.1.4.

4–1

WARNING: The instrument will operate if any button is pressed while "Err 3" is showing. However, because at least one segment or indicator is missing, the display or warning indicators may be incorrect. Continue to use the instrument only in an urgent situation and only if the defective segment(s) has been identified.

- "Err 4" indicates that the N-200 lost power without going through the normal shut-down procedure. Turn the ON/STDBY switch to STDBY and back to ON.

- For software version 2.49 or higher, "Err 5" indicates jumpers W1 and W4 were not installed properly. Contact qualified service personnel or Nellcor's Technical Service Department.

Note: The instrument will operate if any button is pressed while "Err 5" is displayed.

"Err 6" indicates that battery-backed memory contents have been lost, and the trend and event memories were erased and reinitialized. The trend and event memories will operate normally as long as the N-200 is turned on, but when the ON/STDBY switch is set to STDBY, the trend and event memories will be erased. This message may indicate that the RAM socket assembly U15 needs to be replaced. Contact qualified service personnel or Nellcor's Technical Service Department.

Note: This message may also appear briefly when the N-200 is first turned on after the monitor EPROM has been replaced with a different version. No action is required.

For software version 2.5 or higher, "ALL cir" indicates that the trend and event memories were erased and reinitialized. The N-200 erases and reinitializes the memories if the data have been corrupted. The memories can also be manually cleared and reinitialized. In both cases, the "ALL cir" appears. No further action is necessary. When "ALL cir" appears because the memory data were corrupted and erased, a simultaneous 5-second alarm sounds.

Note: If the N-200 erases the trend and event memories, a message header appears on the trend graph indicating that the oldest portion of the memory was erased.

For software version 2.5 or higher, "Err Pb" indicates the powerbase is not communicating

with the monitor. Check that the powerbase is plugged in and the monitor is correctly

installed on the powerbase. If the message does not disappear, contact qualified service

personnel or Nellcor's Technical Service Department.

Note: The instrument will operate if any button is pressed while "Err Pb" is displayed.

- 5. Perfusion indicator is not tracking pulse (PULSE SEARCH indicator is on) and saturation and pulse rate are not displayed.

- The sensor is improperly applied to the patient or it is not plugged in. Check and correct if necessary.

- The patient's perfusion is too poor for the instrument to detect an acceptable pulse.

-check the condition of the patient.

--- use C-LOCK ECG synchronization.

4-2

-test the instrument on yourself or another patient.

-try the nasal OXISENSOR \* R-15.

- The sensor is damaged. Replace with another sensor.

- The patient module is damaged. Try another patient module. If no spare patient module is available, or replacement does not resolve the problem, refer to Sections 3.3 (Patient Module), 3.4.2 (Analog Front End and LED Current Drive), and 5.4 (Processor PCB Tests).

- Perfusion amplitude indicator tracks a pulse but there is no oxygen saturation or pulse rate display.

- The sensor is damaged (red LED). Replace with another sensor.

- The patient's perfusion is too low to allow the instrument to measure saturation and pulse rate (fewer than three or four bars on the perfusion display).

---check the condition of the patient.

-use C-LOCK ECG synchronization.

-test the instrument on yourself or another patient.

-try the nasal OXISENSOR R-15.

Excessive patient motion is making it difficult for the instrument to find the actual pulse pattern.

-use C-LOCK ECG synchronization.

--set the N-200 for Mode 3 (refer to Operator's Manual).

- Patient module cannot be connected to the instrument.

- Incorrect type of patient module is being used. Use a NELLCOR N-200-series patient module.

- The connector pins are bent. Straighten them carefully or replace the patient module (the plug is internally sealed and should not be disassembled).

- 8. Saturation and/or pulse rate display are changing rapidly and pulse amplitude indicator is erratic.

- Excessive patient motion is making it difficult for the instrument to find a pulse pattern.

---use C-LOCK ECG synchronization, or

-if possible, ask the patient to remain still, or

--check whether the sensor is securely applied and replace it if necessary, or

-use a type of sensor that tolerates more patient motion, or

-move the sensor to a site with less movement, or

-use Mode 3 if appropriate. (Refer to the N-200 operator's manual.)

- An electrocautery unit (ECU) is interfering with performance.

- —the ECU cable and N-200 patient module are too close to each other. Move them as far apart as possible.

- the sensor is too close to the ground pad or electrocautery site. Move sensor to a different site if possible.

- —the ECU and N-200 are plugged into a common power source. Operate the N-200 on battery, or plug it into a different AC outlet.